PACS 73.20.-r

# Current transport mechanisms in metal – high-*k* dielectric – silicon structures

### Y.V. Gomeniuk

V. Lashkaryov Institute of Semiconductor Physics, NAS of Ukraine, 41, prospect Nauky, 03028 Kyiv, Ukraine E-mail: yurigom@lab15.kiev.ua

**Abstract.** The mechanism of current transport in several high -k -dielectric, including rare earth metal oxides (Gd<sub>2</sub>O<sub>3</sub>, Nd<sub>2</sub>O<sub>3</sub>), ternary compounds (LaLuO<sub>3</sub>) and rare earth metal silicate (LaSiO<sub>x</sub>) thin films on silicon was studied using current-voltage (I-V) and conductance-frequency ( $G-\omega$ ) measurements at temperatures 100-300 K. It was shown that the current through the dielectric layer is controlled either by Pool-Frenkel mechanism of trap-assisted tunneling or by Mott's variable range hopping conductance through the localized states near the Fermi level. From the results of measurements, the dynamic dielectric constant k of the material, energy positions and bulk concentrations of traps inside the dielectric layers were determined.

**Keywords:** high-*k* dielectric, dielectric-semiconductor interface.

Manuscript received 02.03.12; revised version received 12.03.12; accepted for publication 27.03.12; published online 30.05.12.

### 1. Introduction

Further downscaling in micro- and nanoelectronics motivates the search of a replacement gate dielectric instead of conventional thermally grown silicon dioxide. Reduction of  $SiO_2$  thickness below 1.5 nm is associated with several critical drawbacks, the most important of which is increased leakage current through the gate oxide due to direct tunneling effects. In order to reduce gate leakage while maintaining the gate capacitance, dielectrics with higher dielectric constant than  $SiO_2$ , the so-called high -k dielectrics, are being intensively investigated now. The new materials must provide the same or better control of semiconductor surface properties than that for ultrathin  $SiO_2$  layers, with a much lower level of leakage currents, due to suppression of direct tunneling.

Among high-k dielectrics, epitaxial transition metal and rare earth metal oxides have been considered as perspective materials to replace silicon dioxide for future CMOS technology because of their wide band gap and large offsets between conductance and valence bands of the dielectric and silicon. The complete and broad reviews of future high -k dielectrics for substitution of silicon dioxide can be found in [1-4]. An ideal high -k

gate dielectric must provide a low interface state density, high band offsets at the interface with the semiconductor and low leakage currents. The tunneling components of the leakage current, such as direct tunneling and Fowler-Nordheim tunneling currents, can be substantially suppressed while using the thicker films. But there may be also observed other types of leakage current in the dielectric films, such as, trap-assisted currents in the case when the dielectric contains deep traps in the bulk, or the currents through grain boundaries in the case of polycrystalline film. The crystallization temperature of the silicon oxide exceeds 1000 °C, so that the dielectric film remains amorphous after the high-temperature technological steps of the integrated circuit fabrication cycle. This is not the case for many high -k dielectrics with the crystallization temperature of about 400 °C. Crystallization of the amorphous film deteriorates its dielectric quality due to an increased leakage current through the grain boundaries.

This problem can be solved, at least partially, by the use of epitaxially grown single-crystalline thin layers of rare earth oxide dielectric instead of the amorphous films [5]. But even with the perfect crystalline quality of the dielectric layer and abrupt oxide/silicon interface, the achievement of low leakage currents in high -k-silicon

systems is a problem, because the rare-earth oxides, as most types of the high -k dielectrics, are ionic compounds with relatively weak chemical bonds between ions, and are known to contain a high concentration of oxygen vacancies [1]. These intrinsic defects produce the local energy levels in the band gap, being a reason of relatively high leakage currents. Another possible mechanism of the leakage currents through the high -k dielectric layer is phonon-assisted tunneling, since in higher dielectric constant metal oxides the density of soft optical phonons is high because of ionic bonds [2].

This paper presents the results of current-voltage (I-V), current-temperature (I-T) and a.c. conductance-frequency  $(G-\omega)$  measurements for several high -k dielectrics, including rare earth metal oxides  $(Gd_2O_3$  and  $Nd_2O_3)$ , ternary compounds  $(LaLuO_3)$  and silicate  $(LaSiO_x)$  films, epitaxially grown on silicon substrates.

### 2. Experimental

The single-crystalline Gd and Nd oxide films were grown in an integrated multichamber ultrahigh vacuum system using solid source molecular beam epitaxy (MBE), which allows better control semiconductor/dielectric interface properties and can avoid a low dielectric constant interfacial layer. The details of deposition of metal oxide dielectric films can be found elsewhere [6]. Prior to Pt metal dot deposition, the structures were annealed in forming gas for 10 min at 450 or 500 °C to decrease the charge instability in the dielectrics. Three structures were studied: Pt-Gd<sub>2</sub>O<sub>3</sub>pSi(111) annealed at 500 °C (hereafter denoted as #1), Pt-Gd<sub>2</sub>O<sub>3</sub>-pSi(100) annealed at 450 °C (#2), and Pt- $Nd_2O_3$ -pSi(111) annealed at 450 °C (#4). thicknesses of the oxide layers were equal to 6.7 nm (#1), 7.5 nm (#2) and 10 nm (#4), the dielectric constant k of deposited oxide films was within the range from 11.2 to 11.9.

The dielectric layers in the Pt-LaLuO<sub>3</sub>-pSi(100) MOS structures were deposited by molecular beam deposition (MBD). Evaporation of La and Lu in O<sub>2</sub> was performed at a substrate temperature of 450 °C. Two structures were studied with the nominal physical thicknesses of the dielectric layer (LaLuO<sub>3</sub>) of  $t_{\rm ox} = 6.5$  and 20 nm. The samples were exposed to forming gas annealing at 400 °C for 10 min (10% H<sub>2</sub>). Pt gates were prepared by e-gun evaporation through a shadow mask.

The dielectric layers of the NiSi-LaSiO<sub>x</sub>-pSi(100) MOS structures were deposited onto n- and p-type silicon substrates by electron beam evaporation from La<sub>2</sub>O<sub>3</sub> pellets [7]. The structures were studied with the nominal physical thicknesses of the dielectric layer (LaSiO<sub>x</sub>) of  $t_{ox} = 10$  and 7.5 nm. Circular NiSi electrodes have been fabricated by full silicidation and reactive ion etching [8]. The samples received no post-metallization annealing treatment.

The films were characterized by conductance vs. frequency measurements within the temperature range 120 to 320 K using an Agilent 4284A LCR meter. Current-voltage and current-temperature dependences were measured with Keithley 6485 picoammeter.

#### 3. Results and discussion

3.1. Comparative analysis of a.c. and d.c. conductance in rare-earth oxides  $Gd_2O_3$  and  $Nd_2O_3$

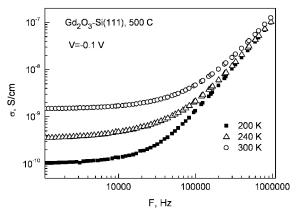

Let us consider first the  $G-\omega$  dependences measured in the structures with Gd<sub>2</sub>O<sub>3</sub> and Nd<sub>2</sub>O<sub>3</sub> dielectrics. Fig. 1 shows the dependences of a.c. conductivity at different temperatures for Pt-Gd<sub>2</sub>O<sub>3</sub>-pSi(111) structure annealed at 500 °C (#1). The presented curves were measured at small forward bias (-0.1 V) at the metal electrode). At frequencies the conductivity is frequency independent and at high frequencies the conductivity obeys the power law relationship, so that the equation for the frequency dependence of the conductivity can be written as  $\sigma(\omega) = \sigma_0 + A\omega^s$ , where  $\sigma_0$  represents lowfrequency, or d.c. conductivity. Such behavior of the a.c. transport is observed in a broad range of materials, including amorphous semiconductors, ionic conductors and heavily doped compensated semiconductors, and is commonly treated either as a dielectric relaxation in solids [9, 10] or as a variable-range hopping (VRH) conductance through the random network of hopping sites [11]. The critical exponent s in most cases is slightly less than or close to unity. The temperature dependence of conductivity at the low-frequency (d.c.) is much more pronounced than at high-frequency, which is also a mark of the hopping process and can be theoretically explained in frames of free-energy barrier model for disordered solids [12].

Rare-earth oxides are known to be good ionic conductors [13]. Ionic conductance takes place via the oxygen vacancies, and although it is usually observed at high temperatures, we can not rule out this mechanism of carrier transport. Theoretical consideration of ionic transport in solids with account of the effect of relaxation of ionic surrounding [14] gives the following equation for a.c. conductivity:  $\sigma(\omega) = \sigma_0[1 + (\omega/\omega_c)^2]$ , so that at frequencies exceeding some  $\omega_c$  the conductance is proportional to the square of the frequency. Our results show that the critical exponent s in the power law approximation of the frequency dependence of conductivity at high frequencies is higher than unity (see Fig. 1), which can not be explained in the frames of dielectric relaxation or hopping conductance theories. One of possible explanations is that the ionic conduction contributes into the observed a.c. conductance at high frequencies. It should also be mentioned, that the presence of grain boundaries in polycrystalline material can enhance the ionic conductance by several orders of magnitude [15] which is confirmed by the theoretical calculations predicting that oxygen vacancies tend to precipitate at grain boundaries [16].

**Fig. 1.** Dependences of a.c. conductivity on frequency at various temperatures.

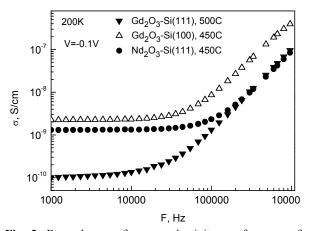

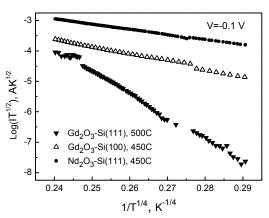

Taking into account the above arguments, we consider the a.c. conductance in the studied systems to be mainly related with the processes within oxide bulk and not at the interface. Fig. 2 shows the dependences of a.c. conductivity on frequency for all the samples. The most remarkable feature is that the structure Pt-Gd<sub>2</sub>O<sub>3</sub>pSi(111) annealed at 500 °C shows the lowest a.c. current at low frequencies. These measurements were supplemented with the measurements of the temperature dependences of d.c. forward current carried out at the same small forward bias -0.1V. Fig. 3 shows the temperature dependences of d.c. current plotted in Mott's coordinates  $\log(\sigma T^{1/2})$  vs.  $T^{-1/4}$ . The current appears to obey the Mott's  $T^{-1/4}$  law that corresponds to the VRH conductance via the localized states at the Fermi level.

The Mott model predicts the following dependence of the conductivity for the variable-range hopping process [11]:

$$\sigma(T) = (\sigma_0 / T^{1/2}) \exp(-B / T^{1/4}), \qquad (1)$$

Fig. 2. Dependences of a.c. conductivity vs. frequency for three samples.

**Fig. 3.** Temperature dependences of the forward current for three structures plotted in Mott's coordinates.

where  $\sigma_0$  is a temperature independent factor,  $B = B_0 \left(\frac{\alpha^3}{k_{\rm B} N(E_{\rm F})}\right)^{1/4}, \ B_0 - {\rm factor \ ranging \ from \ 1.66 \ to}$

2.5,  $\alpha^{-1}$  – localization length of electron,  $k_{\rm B}$  – Boltzmann's constant,  $N(E_{\rm F})$  – the bulk concentration of the localized states at the Fermi level. From the slope B of the  $\ln(\sigma T^{1/2})$  vs.  $T^{-1/4}$  dependence, one can determine the bulk concentration of the localized states near the Fermi level as follows:

$$N(E_{\rm F}) = B_0^4 \frac{\alpha^3}{B^4 \cdot k_{\rm B}} \,. \tag{2}$$

The hopping conductivity through the states at the Fermi level can be additionally described by the following expression [17]:

$$\sigma(T) = 1/6q^2 R^2 v_{ph} N(E_F) \times \exp(-2\alpha R) \exp(-W/k_B T),$$

(3)

where R is the hopping distance,  $v_{ph}$  is the phonon frequency, W is the activation energy of the hopping, and q is the electron charge. In Mott's model, the hopping activation energy is given by the equation [11]:

$$W = \frac{3}{4\pi R^3 N(E_{\rm E})} \,, \tag{4}$$

where the hopping distance

$$R = \left(\frac{3}{2\pi\alpha N(E_F)k_{\rm B}T}\right)^{1/4}$$

.

Assuming the localization radius of the electron wavefunction  $\alpha^{-1} = 10^{-7}$  cm and  $B_0 = 2$  [18], from the slope B of the characteristics  $\log(\sigma T^{1/2})$  vs.  $T^{-1/4}$  presented in Fig. 3 and using Eq. (2) we determine the density of states at the Fermi level  $N(E_{\rm F})$ . The values of bulk density of states  $N(E_{\rm F})$  and of hopping activation energy W for three measured samples are presented in Table. The physical origin of the states being the

hopping sites inside the dielectric layer is still discussed, but most often the deep levels in the high -k materials are associated with oxygen vacancies and interstitials randomly distributed in the dielectric film [1, 13, 19]. The role of oxygen related defects as carrier traps in high -k dielectrics HfO<sub>2</sub> and ZrO<sub>2</sub> is discussed in [20-22]. Theoretical calculations of energy positions of trap levels associated with various charge states of oxygen vacancies for different high -k dielectrics are presented in [23, 24].

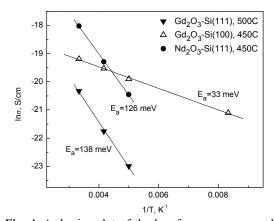

Finally, we have plotted the low-frequency a.c. conductance  $\sigma_0(T)$  in Arrhenius coordinates to check the activation energy. Fig. 4 shows the respective dependences for all the samples. As we have already mentioned, the measurements were carried out at the small forward bias  $V_g = -0.1 \,\mathrm{V}$ . At such low biases, the probability of Fowler-Nordheim tunneling through the triangular barrier or of thermally assisted tunneling of Pool-Frenkel type is negligible. So, the derived values are not related to the valence band offset at the interface. We may suggest that the apparent activation energy is related either to activation of holes from semiconductor to the trap levels in the oxide band gap or to phononinduced excitation of carriers during VRH process inside the dielectric. The values of activation energies  $E_a$ derived from the temperature dependences of lowfrequency a.c. currents are presented in Table. The lowest value of the activation energy  $E_a$  was found for the Gd<sub>2</sub>O<sub>3</sub> film grown on the Si(100) substrate (sample #2). This sample also shows the lowest density of interface states [25].

Table. Bulk trap concentration, hopping activation energy and activation energy from low-frequency a.c. conductance for  $Gd_2O_3$  and  $Nd_2O_3$  dielectrics.

| Sample # | $N(E_{\rm F})$       | W (Mott) | $E_{\rm a}\left(\sigma_0(T)\right)$ |

|----------|----------------------|----------|-------------------------------------|

|          | $[eV^{-1}cm^{-3}]$   | [meV]    | [meV]                               |

| 1        | $2.1 \times 10^{17}$ | 107      | 138                                 |

| 2        | $1.8 \times 10^{19}$ | 37       | 33                                  |

| 4        | $7.8 \times 10^{19}$ | 30       | 126                                 |

**Fig. 4.** Arrhenius plot of the low-frequency a.c. conductivity for three samples.

Taking into account that the applied forward bias during the measurement of temperature dependences is low ( $V_g = -0.1 \,\mathrm{V}$ ) and assuming that the current is due to the transport of holes, the energy levels corresponding to the bulk defect centers in the dielectric should be situated near the Fermi level, which is common for dielectric and silicon. At room temperature for p-type silicon doped with impurity concentration  $5 \times 10^{16} \, \text{cm}^{-3}$ . the Fermi level is situated at 0.13 eV above the Si valence band [26]. The valence band offset at the Gd<sub>2</sub>O<sub>3</sub>/Si interface lies in the range from 2.3 to 2.78 eV [3, 27, 28] in dependence on methods of measurement and at Nd<sub>2</sub>O<sub>3</sub>/Si interface is equal to 2.7 eV [29]. Thus, in Gd<sub>2</sub>O<sub>3</sub> location of the deep levels takes place at 2.5 to 3.0 eV above the valence band edge, and in Nd<sub>2</sub>O<sub>3</sub> the deep levels are situated at 2.9 eV above the valence band edge. Therefore, we can suggest that the current occurs via the transport of holes, which enter the interface levels and then tunnel to the trap levels in the dielectric, with the following VRH conductance process through the random network of localized states in the band gap.

It can be seen from Table that there exists a quite satisfactory correlation of activation energies calculated from a.c. conductance and d.c. current-temperature dependences for samples #1 and #2. Sample #4 with Nd<sub>2</sub>O<sub>3</sub> oxide dielectric shows much lower hopping activation energy as compared to the activation energy obtained from the temperature dependence of lowfrequency a.c. conductivity. This sample is also characterized by much higher concentrations of interface states in the silicon band gap. The reason for this behavior may be the fact that the high concentration of bulk interface states is involved into a recharging process when the sample is tested in a.c. mode. Their contribution to the total a.c. conductance has the activation energy that may differ from that in d.c. measurements.

## 3.2. Transport mechanisms in ternary dielectric compound LaLuO<sub>3</sub>

LaLuO<sub>3</sub> is an attractive candidate as a gate dielectric material because of its low hygroscopicity, high thermal stability, high optical bandgap ( $\sim$ 5.6 eV) and high kvalue close to 30 [30]. I-V characteristics measured on the Pt/LaLuO<sub>3</sub>/p-Si(100) MOS structures have revealed an apparent dependence of the leakage currents on temperature for all the range of reverse and low  $(|V_o|<1 \text{ V})$  forward biases indicating the thermallyactivated charge transport mechanism. For the forward voltage absolute value of about 1 V the temperature dependence of the current vanishes and at higher forward biases it becomes metallic, so that the current decreases with increasing the temperature. Because the behavior of the temperature dependence of I-Vcharacteristics appeared to be different at forward and reverse biases, we analyzed them separately.

Figs 5a and 5b shows the current-voltage dependences for the samples with thicknesses of the

dielectric layers 20 and 6.5 nm, respectively, plotted in Poole-Frenkel coordinates ( $\ln(J/V)$  vs.  $V^{1/2}$ ). The sections where the plots can be approximated by a straight line indicate that the forward-bias current is governed by Poole-Frenkel mechanism for trap-assisted thermally activated transport through the potential barriers lowered by the electric field. This is also confirmed by the current-temperature dependence plotted in Arrhenius coordinates (Fig. 5b, inset).

The voltage and temperature dependences of the current density for the Poole-Frenkel emission mechanism is described by the equation [26]:

$$J \propto V \exp \left[ \frac{q}{k_{\rm B} T} \left( 2a \sqrt{V} - \phi_b \right) \right],$$

(5)

where  $\phi_b$  is the barrier height, q – elementary charge,  $k_B$  – Boltzmann's constant,  $a \equiv \sqrt{q/4\pi k t_{\rm ox}}$ , k – dielectric permittivity,  $t_{\rm ox}$  – dielectric thickness. From the slope S of the  $\ln(J/V)$  vs.  $V^{1/2}$  dependence, one can determine the dielectric permittivity k as follows:

$$k = \frac{q}{a^2 4\pi t_{\text{ox}}}, \ a \equiv \frac{k_{\text{B}}T}{2}S.$$

(6)

Pt-LaLuO<sub>3</sub>-pSi(100) a) ln(J/V<sub>g</sub>), A/ Vcm<sup>2</sup> □ - 100 140 180 · • — 300 -12  $V_{\rm g}^{0.8}, V^{1/2}$ 0.2 0.4 0.6 1.0 1.2 b) Pt-LaLuO<sub>3</sub>-pSi(100) = 6.5 nm-2 In(J/V<sub>G</sub>), A/ Vcm² -3 -12 - 300 ⊆ -6 320 ■ - 340 4 5 6 360 -8 1/T, 10<sup>-3</sup> 1/K -□-380 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 0.2  $V_{\rm g}^{1/2}, V^{1/2}$

**Fig. 5.** Forward current for LaLuO<sub>3</sub> film plotted in Poole-Frenkel coordinates for the 20-nm (a) and 6.5-nm (b) thick oxide layer (inset -I-T dependence in Arrhenius coordinates).

This method gives us the values k = 16 and 20 for the samples with  $t_{\rm ox} = 6.5$  and 20 nm, respectively. For the thinner sample, we have taken for calculation the initial parts of the I-V curves ( $|V_g| < 0.5$  V), so that the electric field in dielectric did not exceed 0.8 MV/cm.

Fig. 6 shows the temperature dependences of the reverse current plotted in Mott's coordinates  $ln(IT^{1/2})$  vs.  $T^{-1/4}$ . The reverse-bias current for both samples appeared to obey Mott's  $T^{-1/4}$  law for variable-range hopping conduction. It can be seen that the dependences are better fitted by Mott's law for the sample with  $t_{\rm ox} = 20$  nm than for that with  $t_{\rm ox} = 6.5$  nm. It could be explained by higher contribution of bulk conductance as compared to the more dominant interface-related conductance mechanism for the thinner oxide sample. From the slope of the Mott plots and using Eq. (2), we can calculate the values of the bulk concentration of the localized states at the Fermi level  $N(E_F)$ . For the thinner sample  $N(E_F) = 4.7 \times 10^{16} \text{ eV}^{-1} \text{cm}^{-3}$  at  $V_g = 1 \text{ V}$  and  $N(E_F) = 2.4 \times 10^{16} \,\text{eV}^{-1} \text{cm}^{-3}$  at  $V_g = 0.5 \,\text{V}$ , and for the thicker one  $N(E_F) = 6.1 \times 10^{16} \,\mathrm{eV^{-1}cm^{-3}}$  at  $V_g = 1 \,\mathrm{V}$  and  $N(E_F) = 4.5 \times 10^{16} \,\text{eV}^{-1} \text{cm}^{-3}$  at  $V_g = 0.5 \,\text{V}$ .

**Fig. 6.** *I-T* dependences of the reverse current plotted in Mott's coordinates for the samples with  $t_{ox} = 20 \text{ nm}$  (a) and  $t_{ox} = 6.5 \text{ nm}$  (b).

© 2012, V. Lashkaryov Institute of Semiconductor Physics, National Academy of Sciences of Ukraine

It should be noted that Pool-Frenkel emission as a dominant mechanism of charge transport in high dielectric constant thin films was reported in several papers [31-34] for ZrO<sub>2</sub>, Eu<sub>2</sub>O<sub>3</sub>, Lu<sub>2</sub>O<sub>3</sub> and HfLaSiON dielectrics. At the same time, variable range hopping conduction in these materials for the first time was observed by our group.

### 3.3. Transport mechanisms in rare-earth silicate LaSi $O_x$

Lanthanum silicate  $LaSiO_x$  has a lower value of k than  $La_2O_3$  oxide, but it offers higher crystallization temperature and lower hygroscopicity. Additionally, the rare-earth metal silicate interface layer can be used as a transition layer between high -k dielectric and semiconductor instead of  $SiO_x$ , thus increasing the total dielectric constant of a gate stack [35]. So, studies of charge carrier transport mechanism in  $LaSiO_x/Si$  structures attract considerable interest.

Fig. 7a, b shows the *I-V* characteristics for 10-nm thick lanthanum silicate layer on *n*- and *p*-Si substrates measured within the temperature range 140 up to 300 K. It can be seen that the forward current densities are rather high. One should notice a different kind of temperature dependence of the forward current for *n*-

and p-Si substrate. The reverse current densities differ by several orders of magnitude for n- and p-type substrates, which can be due to different offsets between conduction and valence bands at the semiconductor/insulator interface. The apparent temperature dependence of the leakage currents is observed for low ( $|V_g|$ <1 V) forward biases indicating the thermally-activated charge transport mechanism.

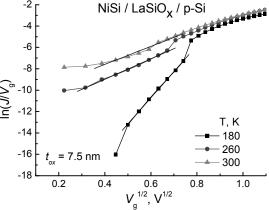

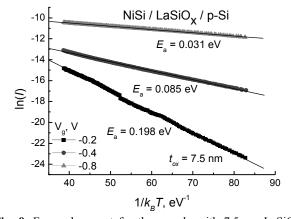

Fig. 8 shows the forward branches of I-Vdependences for the p-type sample with 7.5-nm LaSiO<sub>x</sub> plotted in Poole-Frenkel coordinates ( $\ln(J/V)$  vs.  $V^{1/2}$ ). The sections where linear approximation is valid indicate that the forward-bias current is determined by the Poole-Frenkel mechanism for trap-assisted thermally activated transport. This is also confirmed by the Arrhenius plots of the current-temperature dependences (Fig. 9). At a forward bias, the current inside dielectric is mainly caused by transport of majority carriers, in our case, of holes injected from the semiconductor. The depth of hole traps in respect to the valence band edge was calculated from the slopes of ln(J/V) vs.  $1/k_BT$  plots and equals to  $\phi_b = 0.47$  eV. The dynamic dielectric permittivity k was evaluated from the slopes of ln(J/V)vs.  $V^{1/2}$  plots (Fig. 8) using Eq. (6) and gave the values ranging from 16.3 to 16.8.

**Fig. 7.** *J-V* characteristics for (a) 10 nm LaSiO<sub>x</sub>/*n*-Si and (b) 10 nm LaSiO<sub>x</sub>/*p*-Si structures measured at various temperatures.

**Fig. 8.** Forward current for the sample with 7.5-nm  $LaSiO_x$  layer plotted in Poole-Frenkel coordinates.

Fig. 9. Forward current for the sample with 7.5-nm LaSiO<sub>x</sub> layer plotted in Arrhenius coordinates for various  $V_g$ .

### 5. Conclusions

The mechanism of charge carrier transport through the rare-earth metal oxide films  $Gd_2O_3$  and  $Nd_2O_3$  at a low forward bias was found to be the Mott variable-range hopping conductance through localized states near the Fermi level. This mechanism also determines a.c. conduction at frequencies above 100 kHz. From the measurements of temperature dependences of forward currents, the bulk concentrations of the deep levels in the high -k oxides were determined. These levels are most probably related to the oxygen vacancies, the large concentration of which is inherent to ionic metal oxides. The conduction via these defect levels in the band gap of dielectric may be at the origin of the high leakage currents observed in many high -k materials.

The charge carrier transport and bulk density of states was studied in MBD grown  $LaLuO_3$  oxide which is considered as a perspective high -k dielectrics for micro- and nanoelectronics applications. It was shown that the forward current through the dielectric is controlled by the Poole-Frenkel mechanism of trap assisted thermally activated transport. The mechanism of the reverse current was found to be the variable-range hopping conductance through localized states at the Fermi level. The charge carrier transport through the  $LaSiO_x$  dielectric film was found to occur via Poole-Frenkel mechanism.

### Acknowledgements

This work has been partly funded by the National Academy of Sciences of Ukraine in frames of the Complex Program of Fundamental Research "Nanosystems, nanomaterials and nanotechnologies", project No. 53/32/11-H. Author is grateful to H.J. Osten, M.C. Lemme, A. Laha, P.K. Hurley, K. Cherkaoui, S. Monaghan, H.D.B. Gottlob, M. Schmidt for providing the samples for measurements, and to V.S. Lysenko and A.N. Nazarov for useful discussions and valuable comments.

### References

- 1. J. Robertson, High dielectric constant gate oxides for metal oxide Si transistors // Repts. Prog. Phys. **69**, p. 327-396 (2006).

- H. Wong, H. Iwai, On the scaling issues and high-κ replacement of ultrathin gate dielectrics for nanoscale MOS transistors // Microelectr. Eng. 83, p. 1867-1904 (2006).

- 3. O. Engström, B. Raeissi, S. Hall, O. Buiu, M.C. Lemme, H.D.B. Gottlob, P.K. Hurley, and K. Cherkaoui, Navigation aids in the search for future high-*k* dielectrics: Physical and electrical trends // *Solid-State Electronics* **51**, p. 622-626 (2007).

- 4. P.K. Hurley, K. Cherkaoui, E. O'Connor, et al., Interface defects in  $HfO_2$ ,  $LaSiO_x$ , and  $Gd_2O_3$  high-

- *k*/metal–gate structures on silicon // *J. Electrochem. Soc.* **155**, p. G13-G20 (2008).

- A. Laha, E. Bugiel, H.J. Osten, and A. Fissel, Crystalline ternary rare earth oxide with capacitance equivalent thickness below 1nm for high-K application // Appl. Phys. Lett. 88, 172107 (2006).

- Q.-Q. Sun, A. Laha, S.-J. Ding, D.W. Zhang, H.J. Osten, and A. Fissel, Effective passivation of slow interface states at the interface of single crystalline Gd<sub>2</sub>O<sub>3</sub> and Si(100) // Appl. Phys. Lett. 92, 152908 (2008).

- 7. P. Hurley, M. Pijolat, K. Cherkaoui et al., The formation and characterisation of lanthanum oxide based Si/high-k/NiSi gate stacks by electron-beam evaporation: an examination of in-situ amorphous silicon capping and NiSi formation // ECS Transactions, 11, p. 145-156 (2007).

- 8. H.D.B. Gottlob, T. Echtermeyer, M. Schmidt et al., 0.86-nm CET gate stacks with epitaxial Gd<sub>2</sub>O<sub>3</sub> high-*k* dielectrics and FUSI NiSi metal electrodes // *IEEE Electron. Dev. Lett.* **27**, p. 814-816 (2006).

- 9. S.R. Eliott, A.c. conduction in amorphous chalkogenide and pnictide semiconductors // *Advances in Physics* **36**, p. 135-218 (1987).

- 10. A.K. Jonscher, Dielectric relaxation in solids // J. Phys. D: Appl. Phys. 32, p. R57-R70 (1999).

- N.F. Mott, E.A. Davis, *Electronic Processes in Non-Crystalline Materials*. Oxford, Oxford University Press, 1979.

- 12. J.C. Dyre, The random free-energy barrier model for ac conduction in disordered solids // *J. Appl. Phys.* **64**, p. 2456-2468 (1988).

- 13. N. Imanaka, Physical and chemical properties of rare-earth oxides, in: *Binary Rare-Earth Oxides*, ed. by G. Adachi, N. Imanaka, Z.C. Kang. Dordrecht, Kluwer Acad. Publ., 2004.

- 14. J. Bisquert, V. Halpern, F. Henn, Simple model for ac ionic conduction in solids // J. Chem. Phys. 122, 151101 (2005).

- 15. X. Guo, S. Mi, and R. Waser, Nonlinear electrical properties of grain boundaries in oxygen ion conductors: acceptor-doped ceria // Electrochem. and Solid-State Lett. 8, p. J1-J3 (2005).

- K.P. McKenna, A.L. Shluger, Electronic properties of defects in polycrystalline dielectric materials // Microelectr. Eng. 86, p. 1751-1755 (2009).

- 17. P. Nigels, Electronic transport in amorphous semiconductors, in: *Amorphous Semiconductors*, ed. by M.H Brodsky. Berlin, Springer-Verlag, 1985.

- 18. H. Böttger, V.V. Bryksin, Hopping conductivity in ordered and disordered solids (I) // *Phys. stat. sol.* (b), **78**, p. 9-56 (1976).

- 19. D. Misra and N.A. Chowdhury, Charge trapping in high-k gate dielectrics: a recent understanding // *ECS Transactions*, **2**, p. 311-328 (2006).

- 20. S. Guha and V. Narayanan, Oxygen vacancies in high dielectric constant oxide-semiconductor films // Phys. Rev. Lett. 98, 196101 (2007).

- J.L. Lyons, A. Janotti, C.G. Van de Walle, The role of oxygen-related defects and hydrogen impurities in HfO<sub>2</sub> and ZrO<sub>2</sub> // Microelectr. Eng. 88, p. 1452-1456 (2011).

- 22. J.L. Gavartin, D. Muñoz Ramo, A.L. Shluger, G. Bersuker, and B.H. Lee, Negative oxygen vacancies in HfO<sub>2</sub> as charge traps in high-*k* stacks // *Appl. Phys. Lett.* **89**, 082908 (2006).

- 23. K. Xiong and J. Robertson, Oxygen vacancies in high dielectric constant oxides La<sub>2</sub>O<sub>3</sub>, Lu<sub>2</sub>O<sub>3</sub>, and LaLuO<sub>3</sub> // Appl. Phys. Lett. **95**, 022903 (2009).

- 24. D. Liu, S.J. Clark and J. Robertson, Oxygen vacancy levels and electron transport in Al<sub>2</sub>O<sub>3</sub> // *Appl. Phys. Lett.* **96**, 032905 (2010).

- 25. Yu.V. Gomeniuk, Determination of interface states in high-*k* dielectric-silicon system from conductance-frequency measurements // Semiconductor Physics, Quantum Electronics and Optoelectronics, 15, p. 1-7 (2012).

- 26. S.M. Sze, *Physics of Semiconductor Devices*. New York, John Wiley & Sons, 1981.

- A. Fissel, M. Czernohorsky and H.J. Osten, Characterization of crystalline rare-earth oxide high-K dielectrics grown by molecular beam epitaxy on silicon carbide // J. Vac. Sci. Technol. B24, p. 2115-2118 (2006).

- 28. M. Badylevich, S. Shamuilia, V.V. Afanas'ev, and A. Stesmans, A. Laha, H.J. Osten, and A. Fissel, Investigation of the electronic structure at interfaces of crystalline and amorphous Gd<sub>2</sub>O<sub>3</sub> thin layers with silicon substrates of different orientations // Appl. Phys. Lett. 90, 252101 (2007).

- 29. A. Fissel, Z. Elassar, O. Kirfel, E. Bugiel, M. Czernohorsky, and H.J. Osten, Interface formation during molecular beam epitaxial growth of neodymium oxide on silicon // J. Appl. Phys. 99, 074105 (2006).

- 30. J.M.J. Lopes, M. Roeckerath, T. Heeg et al., Amorphous lanthanum lutetium oxide thin films as an alternative high-*k* gate dielectric // *Appl. Phys. Lett.* **89**, 222902 (2006).

- 31. W.K. Chim, T.H. Ng, B.H. Koh, W.K. Choi, J.X. Zheng, C.H. Tung, and A.Y. Du, Interfacial and bulk properties of zirconium dioxide as a gate dielectric in metal-insulator-semiconductor structures and current transport mechanisms // J. Appl. Phys. 93, p. 4788-4793 (2006).

- 32. A.A. Dakhel, Poole-Frenkel electrical conduction in europium oxide films deposited on Si(100) // *Cryst. Res. Technol.* **38**, p. 968-973 (2003).

- 33. C. L. Yuan, P. Darmawan, M.Y. Chan and P.S. Lee, Leakage conduction mechanism of amorphous Lu<sub>2</sub>O<sub>3</sub> high-k dielectric films fabricated by pulsed laser ablation // Europhys. Lett. 77, 67001 (2007).

- 34. H.-M. Kwon, W.-H. Choi, I.-S. Han, M.-K. Na, S.-U. Park, J.-D. Bok, C.-Y. Kang, B.-H. Lee, R. Jammy, H.-D. Lee, Carrier transport mechanism in La-incorporated high-*k* dielectric/metal gate stack MOSFETs // Microelectr. Eng. 88, p. 3399-3403 (2011).

- 35. K. Matano, K. Funamizu, M. Kouda, et al., Electrical characteristics of rare earth (La, Ce, Pr and Tm) oxides/silicates gate dielectric // ECS Transactions, 27, p. 1129-1134 (2010).